һ�N��ߖ��������늳����ķ���

������90 nm ���g���c�_ʼ�����x�ӵ���SiON �������ӱ��V���������M��CMOS �������졣������ySiO2 �������ӵ�������ϣ�SiON ����������������^�ߵ���늳���������Ч��������ȖŘO���sԭ���ږ��������еĔUɢ�����������˻�̎��(Post Nitridation Anneal, PNA)���Ƃ���x�ӵ���SiON�������ӵ�һ����Ҫ���E����Ҫ�����ޏ;���p�����γɷ���Si-N �I��ͬ�r�������Շ���ͨ�^����Ķ��������������ޏ�SiO2/Si ����ēp��������ͨ�^�����y�����Ƃ乤ˇ��PNA ��һ�ߜ��˻�ˇ�Ĝضȡ����w�Շ��M�Ѓ������ṩ��һ�Nͨ�^��ߖ�������ĵ�����������߽�늳����ķ����������������c���y���Ƃ䷽����ȣ����ñ��������Ƃ��SiON ���������е������������30%���ϣ���������B��늺ɿɜp��һ����������PMOS ������NBTI ����t0.1% ��t50%�ɷքe���15.3% ��32.4%��

1������

��������Ҏģ�����·(VLSI)���ش�Ҏģ�����·(ULSI)�Ŀ��ٰlչ���������ӹ����g������������Ҫ������MOS ���������ߴ��M��{�וr�����������ӵ�Ҫ�����һ�����@�����𡣖������ӵ��Ƃ乤ˇ�ǰ댧�w���칤ˇ�е��P�I���g��ֱ��Ӱ푺͛Q����������늌W���ԺͿɿ��ԡ�

����MOSFET�������P�I����ָ�����������������Ĵ�Сȡ�Q�ږŘO��ݡ��ŘO����c�ŘO����e�����ȣ��c�Ž��|��ȳɷ��ȡ���ˣ�ͨ�^���ӖŘO����e�ͽ��͖Ž��|��Ⱦ�����ߖŘO��ݣ������͖Ž��|SiO2 �ĺ�Ⱦ�׃�����MMOSFET ����������ߵ���Ҫ�ֶΡ�

���������댧�w���g�M��90 �{�וr���ԁ������y�μ�����SiO2 ��ȵķ���������ǰ��δ�е���������@�r��Ž��|SiO2 �ĺ���ѽ��ܱ�(<20 �)���ŘO©����е��������C���ѽ����������á��S��SiO2 ��ȵ��Mһ�����ͣ��ŘO©���Ҳ����ָ����ʽ���L���Ž��|���ÿ����2�ŘO©����͕�����10 ������һ���棬�ŘO��SiO2 �Ž��|���r��֮�g�����s�|�ĝ���ݶȣ��S���Ž��|��ȵIJ��ཱུ�ͣ��ŘO��������s�|���ĖŘO�ДUɢ�����r���л��߹̶��ږŽ��|�У��@��Ӱ��������ֵ늉����Ķ�Ӱ����������ܡ��\Ȼ�����ӖŽ��|��ȿ�����Ч���ƖŘO©����͖ŘO���s�|�ĔUɢ�����Ǿ��w������������D���t�r�g���P�I����Ҳ������ۿۡ��@�N������͖ŘO©늌��Ž��|���Ҫ���ϵ�ì�ܣ����ڂ��y��SiO2 �Ž��|�����ǟo���رܵġ�

C = e0KA/t

�������У�C = �ŘO���;e0 = �ڿ՚��е������;K= ���ϵĽ�늳���;A= �ŘO����e;t= �Ž��|��ȡ�

�����ĖŘO��ݵĹ�ʽ���҂����Կ������ŘO��ݲ��Hȡ�Q�ږŘO����e�͖Ž��|��ȣ�߀ȡ�Q�ږŽ��|�Ľ�늳������ʜp�ٖŽ��|��Ȳ�����ߖŘO��ݵ�Ψһ��������ʹ�Ž��|��ȱ��ֲ�׃����ߖŽ��|�Ľ��ϵ��K Ҳ���_������EOT �����ӖŘO��ݵ�Ч������ˣ������ߖŽ��|�Ľ��ϵ��K�ɞ��ˮ���֮����

�����ڬF�A�Σ���ߖŽ��|�Ľ��ϵ���ķ��������Ѓɴ��

����һ��Dz���ȫ�µĸ߽��ϵ���IJ�������Ž��|���絪�����x��(HfSiON)�ȡ�������ȫ�²����漰���ŘO���ϵ��x������ƥ�估�ع��g�̵�һϵ�й�ˇ���Ɇ��}�����g�_�l���������^�L�����������M��45 �{���g����������ͬ�rȫ�²����ڼ��g���c��ǰ��ˇ���^�������g���µijɱ��^�ߡ�

������һ��t�Ա���SiO2 ����Ž��|��ͨ�^SiO2����Ĥ��뵪ʹ֮�ɞ����ܵ�SiON ����ߖŽ��|�Ľ��ϵ���������y�Ž��|SiO2 ��K ֵ��3.9��������Si3N4 ��K ֵ���_��7��ͨ�^���s���Ķ��ٿ��Ԍ��F��SiON �Ž��|���ϵ�����õ�Ŀ�ġ���ԭ�ӵē���߀����Ч��������ȖŘO���sԭ���ږŽ��|�еĔUɢ��ͬ�r��ԓ������Ȼ����SiO2 ����Ž��|�����w������cǰ�ڼ��g�����õ��B�m�Ժͼ����ԡ�

����Ŀǰ�I��ͨ�������N��Ҫ�ķ����Ɍ��FSiO2�еĵ����s���γ�SiON��

������һ�N��������SiO2 �����L�^����ͨ��NO �Ⱥ������w���Ķ������L�^����ֱ�ӓ��뵪�����@�N�������s�ĵ������Ժ��y���ƣ������m���댧�w���a��Ҫ��

�����ڶ��N��������SiO2 ���|���L��ɺ�����NO/N2O �Ⱥ������w�h�����Mһ���˻���k�����s�����@�N��������ĵ�ԭ�����۷e��SiO2 �͜ϵ��Ľ���̎���Ķ����ϵ����d���ӵ��w���ٶȮa��ؓ��Ӱ푡�

���������N��������SiO2 ���L�Y����ͨ�^���x���w���F�����s��ԓ��������ĵ�ԭ�ӝ�ȸߣ��������Ҫ�ֲ��ږŽ��|���ϱ�����h�xSiO2/ �ϵ����棬��Ŀǰ�댧�w�I��V�����ܵ���ߖŽ��|���ϵ���ķ���������w��ˇ�������M�ɣ�

����1)����ISSG(In-Situ Steam Generation)ԭλˮ���������������LSiO2 ���|��;

����2)����DPN(Decoupled Plasma Nitridation)������x���w��SiO2 ���|���s��;

����3)����PNA(Post Nitridation Anneal)�ߜ��˻�ˇ����N ���s���ޏͽ��|�еĵ��x���w�p����

�����������Ƃ乤ˇ�У����ږŽ��|�Г���ĵ�ԭ�ӝ�ȸ�����Ҫ�ֲ��ږŽ��|���ϱ��棬��ˌ����mPNA �ߜ��˻�ˇ�Ĝضȡ����w�Շ��͕r�g�g����횇�����ƣ��Է�ֹ���������Ӻ��ЙC�����������s��ɵ�Ӱ�;���⣬PNA �ĸߜ��˻�ˇ��������ɱ��浪ԭ�ӵē]�l������ʹ��ԭ�ӫ@���������^�m�Uɢ����ɲ��ֵ�ԭ�Ӿ۷e��SiO2/Si ����̎���Ķ����ϵ����d���ӵ��w���ٶȮa��ؓ��Ӱ푡�

�������Č������Ƃ乤ˇ��PNA �Ć�һ�ߜ��˻�ˇ�Ĝضȡ����w�Շ����˃������ṩ��һ�Nͨ�^��ߖ������ﵪ������������늳����ķ�����

2�����͜yԇ����

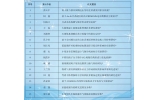

����������300 mm��P ��(100)�辧�A�������8��12Ω-cm����������ˇǰ����Ƭ�����M�И˜���ϴ���������Ӳ���AMAT Centura ACP �����˻��O���Ƃ䡣

�������Ȍ������П����������͟�̎�����������γɾ��з����;����Ŀ�˺�ȵ�SiO2 ��������;���ͨ�^���x���w�������g������SiO2 ���������M�е���ע�룬ʹSiO2 �еIJ���O ԭ����N ԭ��ȡ���γ�Si-N�I���Ķ�������SiO2 ���������{�������һ������Ⱥͽ�늳�����SiON ��������;Ȼ��ͨ�^�ߜ�(1000��-1100��)�ͼ����Ԛ��w(��N2 ��) �Շ���SiON ���������M�е���̎�������ޏ;���p�����γɷ���Si-N �I���Ķ��γɷ����ĵ������ͽ�늳���;����ڵ͜�(500��-800��) �ķՇ���SiON ���������M��������̎�������ޏ�SiO2 / Si ���档

�����������Ӻ�Ⱥ͵���������Revera RVXTM1000X-Ray Photoelectron Spectroscopy �y���ͱ������������ӽ���B����SEMILAB FAaSTR 350 ��y���ͱ�����PMOS ������NBTI (Negative Bias Temperature Instability)��������Agilent 4072 ��y���ͱ�����

3�����Y������

���������еĵ���Ҫ����DPN ��ˇͨ�^������x���w��SiO2 ���|�Г��s���팍�F���䵪������Ҫ��DPN �Ĺ�ˇ�l����Q�������Ӗ����еĵ�������������ߖ����Ľ�늳��������͖�����©�����ͬ�r��������Խ���䌦������ȖŘO���sԭ���ږŽ��|�ДUɢ������ҲԽ������ˣ������F�й�ˇ�l������ߖ����еĵ������ɞ�һ���O�����е�Ҫ��

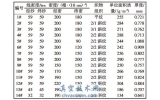

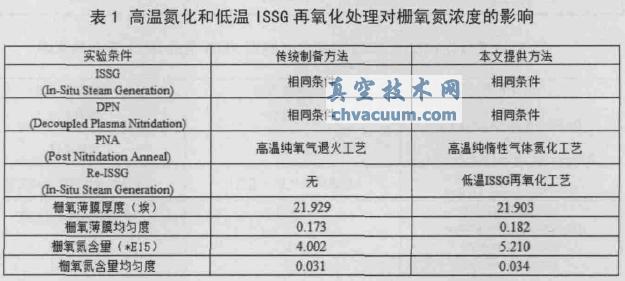

������1 ����øߜص����͵͜�ISSG ������̎�����������ȵ�׃���������������ڱ�����ͬDPN ��ˇ�l���£��c�H�H���Æ�һ�ߜؼ������˻�̎����ˇ��ȣ�����ߜص����͵͜�ISSG ������̎�������е���ȿ������30%���ϡ����Y���������ߜؼ����������������ӓ��s���c����I�Ď��ʣ������ڴ��M�����е����I�Ϻͷ��������Ԍ��F�ڬF�й�ˇ�l������ߖ��������늳����������늳����M�о��_���õ�Ŀ�ġ�

����DPN ���x���w�ڌ��Ž��|�M�е����s��ͬ�r���������ӵ���ײ�����Ž��|�a���p��������65 �{�����¼��g���c���ԣ��Ž��|��������^�������x���w�еĸ������Ӵ��Ž��|ֱ�ӓp���ϵ��������Σ�U�������ӣ���횲��ø��M�������Խ�Q��

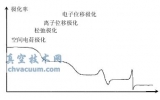

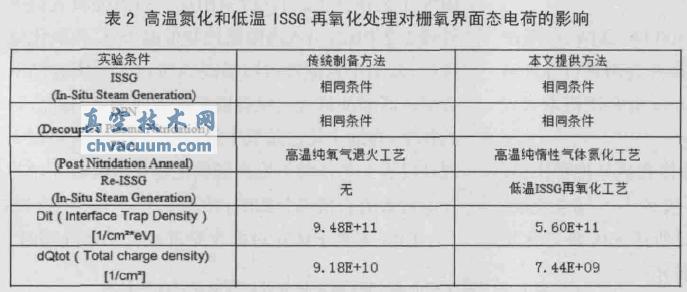

��������ͨ�^�ߜغͼ����Ԛ��w(��N2 ��)�Շ���SiON ���������M�е���̎�������ޏ�DPN ��ˇ����ɵľ���p�����γɷ���Si-N �I���Ķ��γɷ����ĵ������ͽ�늳���;Ȼ���ڵ͜ص������Շ���SiON ���������M��ISSG ������̎��������ԭ�����ď��������Á��ޏ�SiO2/Si �Ľ���ȱ�ݣ��Y�����2 ��ʾ�������������c�H�H���Æ�һ�ߜؼ������˻�̎����ˇ��ȣ�����ߜص����͵͜�ISSG ������̎����������Si/SiO2 ����B�õ�����Ч�ĸ��ƣ������B��늺ɜp����һ�������������Y���������ߜص����͵͜�ISSG ������̎������Ч���Ɩ����Ľ���B��

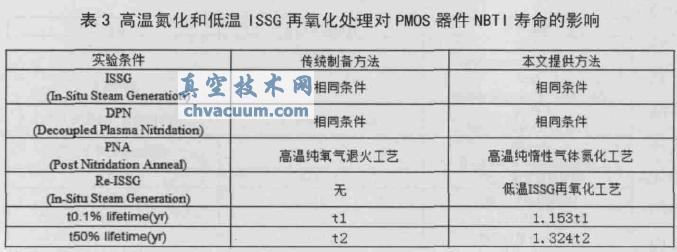

������ǰ��������DPN ��ˇ������ߜص����͵͜�ISSG ������̎����õ��Ė������ﱡĤ�w��ȱ���٣�����B��Ҳ���^С�������ﱡĤ���|�����^�ߡ���3 ��ߜص����͵͜�ISSG ������̎�팦PMOS����NBTI ������Ӱ푡������������c�H�H���Æ�һ�ߜؼ������˻�̎����ˇ��ȣ�����ߜص����͵͜�ISSG ������̎���������ӵ�0.1% ��t50%�քe�����15.3%��32.4%�����Y���������ߜص����͵͜�ISSG ������̎������Ч����PMOS ������NBTI ���ܡ�

4���YՓ

��������ͨ�^�����y�����Ƃ乤ˇ��PNA ��һ�ߜ��˻�ˇ�Ĝضȡ����w�Շ����˃������ṩ��һ�Nͨ�^��ߖ������ﵪ������������늳����ķ��������ñ����ṩ�ķ����Ƃ��SiON �������Ӳ��H���з����ĵ���������������Ч��ߖ������ﵪ����30%���ң��Ķ�ʹ���Ƃ�Ė�����������^�ߵĽ�늳��������F�ˌ�SiON �Ž��|���ϵ�����_���õ�Ŀ�ġ�ͬ�r�����ñ��������Ƃ��SiON �������ӽ���B��늺ɿɜp��һ����������PMOS ������NBTI ����t0.1% ��t50%�ɷքe���15.3% ��32.4%��