�������象Ĥ���e��������Ч�ʵĜy���c����

�������ˌ��F�ͳɱ����象Ĥ�ĸ��ٳ��e����Ҫ�M���ܵă�����ˇ�������e����߹�������Ч�ʌ��ڽ������a�ɱ����Լ���߹�ˇ�����Զ�������Ҫ�����x�����Ќ����l���x���w�������W������eϵ�y�ĸ����ֹ��������M���˜y���c�������l�F���H�����x���늵Ĺ��������ʃH��10%���£� ǻ�ҵļ�������������Ĺ���ռ30%���ң��Ҽ���늿��ֲ���r��ƥ�����Ĺ�������Ӱ��^��ͨ�^��ϵ�yӲ���ĸ��죬�����˼���늿���Ӱ푣��@��������˹������Ч�ʣ��ڸ߷����≺�l���µĹ����������_��60%���ϡ�

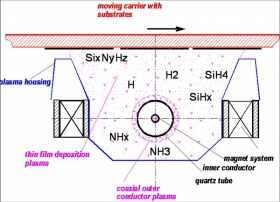

�����齵�����Ĥ̫�늳ؽM���ijɱ��������a��������Ҫ����M����e����߮a�ܣ��@��ҎģЧ�档�@�����x���w�������W������e(PECVD) �O������˸��ߵ�Ҫ�����C�������M����e�ϣ���Ĥ�ĺ���Լ����ܝM��һ���ľ�����ָ�ˡ��c��ͬ�r������������aЧ�ʣ���Ҫ���������ٵij��e��Ĥ,�@����Ҫ�O���܉��ṩ��������l���ʣ��@һ����ͨ�^�����늘O�Y���OӋ���ڝM�������Ҫ���ͬ�r�����܉�ʹ���O����иߵ���������Ч�ʣ�������l�ጧ�µĹ�ˇ�������Եĝ����L�U�������lPECVD ϵ�y�У��������迹ƥ��W�j�����������Ч�ʞ飬�M����ˣ����l�Դݔ���Ĺ����У������x���w�x�������ĵĹ���10% ~ 50% �������ֹ��ʱ�ƥ��W�j�Լ�ϵ�y�ļ���늿������ġ�������ǻ�ҽY���ď��s�ԣ�ƥ��W�j���OӋ���^���죬���Ը��M�ĵط����࣬����L ��ƥ��W�j��P�;W�j�Y���܉����15%���ҵ�����Ч�ʡ�

��������ͨ�^�о�ǻ�Ҽ���늿������ʓp�ĵ�Ӱ푣���ǻ�ҽY���M�Ѓ����OӋ�����ͼ���늿��������ϵ�y����Ч�ʡ�

1������

����PECVD ϵ�y�У����l�������l�Դ��ݔ������ͨ�^ͬ�S��|��ݔ��ƥ������ݔ��ˣ�ƥ�����{��ǻ�ҵ��迹ZM ʹ֮�c����Դ���迹Zg ƥ�䣬���鹲ܗ����ZM = Z*g ������������ʂ�ݔ��ǻ���С���ƥ������ݔ�����cǻ��ͨ�^һ���^�̵�ͬ�S��|�B�ӡ������Դ�ă���Zg �Լ������ɶ�ͬ�S��|�������迹ZT1��ZT2����50�W��ƥ��������# ��ƥ��W�j������Ԫ��ֵ���ǿ��{�ġ����x���w�ĵ�Ч늿�Zp��ǻ�w�ļ����迹Zs������ͬ�S��|�ēp�ģ��t�Դ��ݔ������P i ����ƥ������ݔ�빦�ʣ�����ƥ�����ēp��PM �cƥ������ݔ������Po ֮��,

Pi= PM+ Po (1)

������Po���x���늵��x���w�����Ĺ���PGD�Լ�ǻ�Ҽ���늿������Ĺ���Ps֮�ͣ���

Po= PGD+ Ps (2)

�������˸��Ӝʴ_�Ĝy���@�õ��x���w���H���ĵ���Ϲ��ʣ�ͬ�r�����˹���Ӌ�Լ�V-I ̽ᘷքe�����l�Դݔ���˿�A��ƥ����ݔ��˿�B ��ƥ����ݔ���˿�C �M�Мy�����y��֮ǰ���Ȍ�ƥ������λ���M���{����ʹƥ����ݔ��˿�B ̎�y�����ķ���ϵ����С(С��1.5) ���ڴ˺��εĜy���У�ƥ�����ĸ�Ԫ��λ�ñ��ֲ�׃��ͬ�r�{������Դʹ��ݔ�������c���书�ʲ�׃���ڷքe�y��A��B ��C �˿ڵĹ��ʺ���Ӌ���ͬ�S��|��ƥ�����Ĺ��ʓp�ġ����˷���Ĝy��ϵ�й�ˇ�l�����x���늵��x���w���ĵĹ��ʣ���Godyak�����һ���l���µķ�����Ĺ��ʵĜy�������M���˸��M�����w����:

����(1) �ڱ��Cϵ�y�����l����늵ėl��( ��ʹǻ���б��ֳ�����ջ��≺��B) �y��늘O늉�Vo�c���l����Ps�����L��늉�-�����������Q����ʹ���������

����(2) ��Ŀ�˹�ˇ�l���y���x���늕r��늘O늉��Լ��˕r�Ĺ�������P0���˕r�ڻ��ʹ����������ҵ�����늉��Ĺ���ֵ���c֮���p���õ��x���늵����Ĺ���PGD��

�����������y���^���У������C����늘O�g���ڃȵ�ϵ�yӲ�����õ�һ���ԣ���ϵ�y��������׃���r,������y�����ʹ����������������ґ���ע��,��̎����ʹ�ù���Ӌ�y������鹦��Ӌ�y�����ʵ�ԭ��Ҫ��ؓ�d���M��50�W�����迹�ėl������t�������^���`������ڴ���������ǻ�Һ��y�M�������l����ͬ�r������f�����y�����������C���Ĺ��ʣ����Ƕ��μ������ϵ��C���������ĵĹ��ʱ��^С��ʹ��V-I ̽ᘜy���r������Բ�Ӌ���ɴ˿��ܮa��10% ~ 20%���`�

�YՓ

����С��ePECVD �O���У����������ʱ��^�ͣ����ǻ�Ҽ���늿������ƥ��������^��������^������Ĺ���������ƥ�����У��@���ֹ��ʿɳ��^70%���ϡ�ͨ�^���Ƽ���늿��ķֲ���r��������߹����������_��60% ���ϡ����ʵ��������c늘O늉����P���S��늘O늉�����ߌ��_�����ֵ����څ��͡�