SOI��gֵ����ʽ���ٶȂ������c��ˇ���F

��������SOI ���g������늸���ϵ��x���w����ӹ����OӋ�Ƃ���һ�N����ƽ�����Ӹ�g ֵ����ʽ���ٶ�Ӌ��ԓ���ٶ�Ӌ����X �S���cY �S���Ԫ���������������|���Kƽ�����ӽY�������Q�IJ��ַ�ʽ����Ч���������`���ȵĽ���ɔ_������˂������Ĝy�����ȡ��yԇϵ�y���������ٶȂ��������`������1.170 LV/ g ���о�����ԓ���ٶȂ������Ɍ��F�����̸��_25× 104g ���ٶȵĜy����

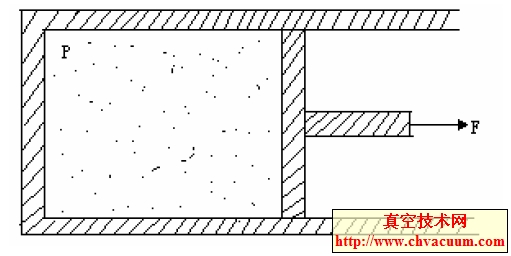

�����C�ϵ�y( MEMS) ���ٶȂ�������һ�N��Ҫ�đT�Ԝy�������������w�eС�������p��푑��졢���ڼӹ��ȃ��c��Ŀǰ�яV����������܇�����պ��졢܊�µ��I�����и�g ֵ���ٶȂ�������܊���I����зdz���Ҫ�đ��Ãrֵ�����Ը�֪�������w�Р�B��ӲĿ���֏ؕr�a���ě_�����ȡ��ھ����^��T���d�ɵ�܊�È��ϣ���Ҫ�y���ļ��ٶȸ��_���f������ʮ�f���ٶȣ��@��Ҫ����ٶ�Ӌ���H��Ҫ�ߵ��`���ȣ�߀Ҫ���иߵ��C���l���c���_��������

����Ŀǰ�Ї��ڸ�g ֵ���ٶ�Ӌ�о������c����߀�����^���࣬���ڇ���ԓ�I��ļ��g���i,������Ҫ�аl���ɑ����ڄӑBײ���^�̼������\���^���Л_���d�ɜy���ĸ�g ֵ���ٶȂ�������ᘌ�Ŀǰ���պ��죬�e�nj������ŵ�܊���I��g ֵ���ٶȂ��������������������SOI ���ϵĿ�ݗ�䡢���ߜصȐ��ӭh���Լ����ĵ����c����ǰ���о��Ļ��A�ϣ����Č��H�Ƃ��˶��Sƽ�����ӡ�����SOI ��Ƭ�ĸ�g ֵ����ʽ���ٶȂ�����������SOI �όӹ�������˹ͨ늘��pU ����������裬ͬ�r�������ڿɄӲ����ϲ���; ����Ԫ����������g���øߜؽ��|��(SiO2 ��) ���F늸��x,��Q���y�댧�w�������������^���м���PN �Y©�������ɵĜ�Ư���}; ���Ä����^������ұ��������������|���K���������˽Y���Ŀɿ��Ժ��`���ȡ�ǰ��ģ�M�о��ͱ��ĵČ������������OӋ�ļ��ٶ�Ӌ�����^�ߵ��`�����c�C���l�ʣ������^��Ŀ��_���������ɝM���طN�h�������_25 ×104g ���ٶȵĜyԇ����

1����g ֵ����ʽ���ٶȂ������ĽY���c�Ƃ�

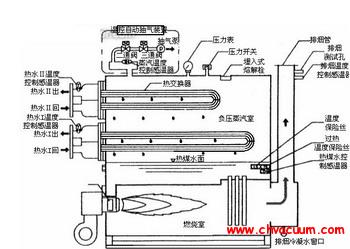

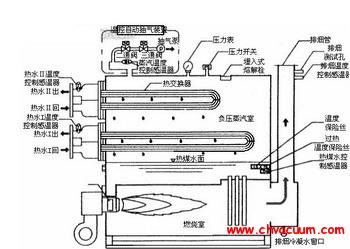

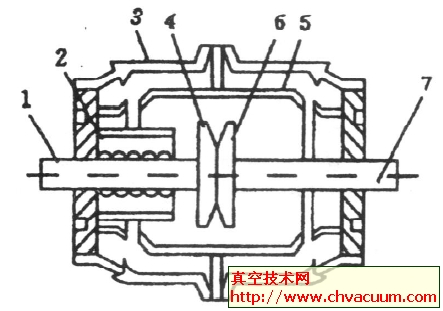

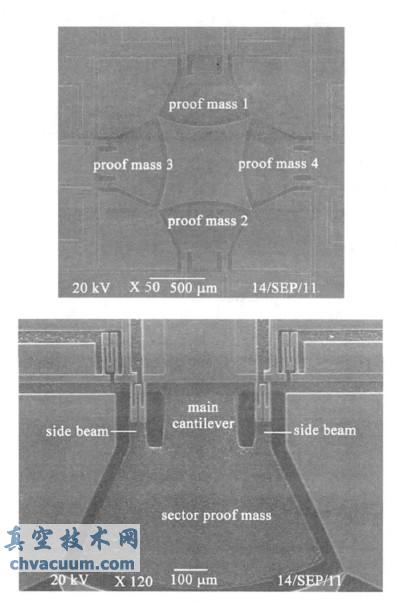

���������OӋ�Ķ��Sƽ������SOI ��g ֵ���ٶȂ����������ɃɌ������Ă���Ԫ��ÿһ���Y����Ԫ�����ұ������ɂ�����֧��U �͉������Ă��������������|���K���ɂ��pU �͉������̓ɂ�������蘋�ɻ�˹ͨ늘�M�ɣ����H�Ƃ�Ă�������D1 ��ʾ��

�D1 SOI ��g ֵ����ʽ���ٶȂ�����

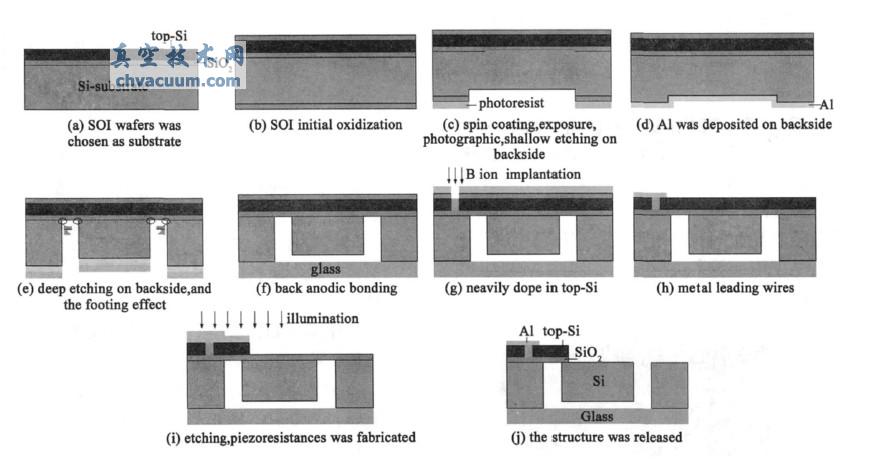

�����Ƃ乤ˇ�^����ע�⣺ �ߜع�ˇ��������ѭ�� �ȸߜع�ˇ����͜ع�ˇ�����ٻ����������п�����ԓ�����ڻ����c�������Ϲ��ڵĸߜع�ˇ֮��»���ǰ�������C��Ƭ����]�и���ȵ��_�A�����g�Ƿ����댧������ʧЧ���s�|�x�ӡ����ϵ��x���Ƿ����ɼӹ��O�����Ⱦ��ԓ���ٶȂ������ļӹ��Ƃ�ֻ����K��Ĥ�壬���H�Ƃ乤ˇ�^�����£�

����( 1) ��Ƭ�� �ʂ�һ�K�p�撁���SOI ��Ƭ���ӹ��Ȟ�300 um��SiO2 �Ӻ�Ȟ�1 um���ό�p+ ���Ȟ�2~ 3 um������ʞ�0.005~ 0. 008 �Wķ.cm��

����( 2) ������ ��SOI ��Ƭ�M�П�������

����( 3) ���z�����( һ�ι��) �� ���ӹ�����Ϳ���z�����õ�һ�K��ģ�匦����z�M�й�̡��@Ӱ�������ٿ��g�����ӣ��������������o�ӣ����g�ӹ裬�γɱ���\�ۡ����g5 um �\�ۣ�����mጷŽY���γɿɄӲ�����ԓ�Ӱ�D��ؓ�棬ͬ�r�ѽY���Ą�Ƭ�۴��_��

����( 4) ������e�X�ӣ� ���ϲ���Ƭȥ�z��ϴ������e�����X�ӡ�

����( 5) �������( ���ι��) �� ���ϲ���ˇ����ӹ��X���Ͻ��^���z��ǰ�桢��̡��@Ӱ�ͺ����X���M�п��g�������X�����鱣�o�ӣ����g�ӹ裬�γ��|���K���|���K�c���ұ�����ԓ�Ӱ�D��ؓ�棬���g�^���Ȟ�30 um��

����( 6) �I�ϣ� ���ϲ���Ƭ�M��ȥ�z����ϴ����ˮ��̎���������I�ϼ��g���M���ӹ��c�������I��,������w��ķ��b��

����( 7) �ؓ��s�����ι�̣� �όӹ��_�ס����όӹ��M���ؓ��s���γɚWķ���|�^���_�׳ߴ��8 um ×8um��ԓ����ģ���ؓ�棬�c�ڶ��Ӱ��M���̣����]����^���٣��y���ʣ�ԓ����ģ����_��Ƭ�^�����όӹ��M�Є��z��ǰ�棬���õ����K��ģ���M�й�̡��@Ӱ������̎�����g�����ӣ������������鱣�o�ӣ��M��B �x�ӵ�ע�롣

����( 8) �����������g( �Ĵι��) �� ���ϲ���Ƭ�M��ȥ�z����ϴ��̎�����eһ�ӽ����X�����M�Є��z,���õ��ĉK��ģ���M�й�̣��M�^����һϵ��̎�����g�����X���γ��X���������н��پ�������С��20 um��늘O�ߴ��200 um × 300 um��늘O֮�g���g����250 um�����پ�֮�g����С�g����14 um��ԓ�Ӱ�����棬�c�ڶ��Ӱ��M���̌��ʡ�

����( 9) �������l����( ��ι��) �� ���ϲ���Ƭ������Ϳһ�ӹ���z�����õ���K��ģ���M�й�̣����^�@Ӱ�����g�όӹ�Ƭ���γɉ������^��������Ч�pС����늘O�������裬�c�ϲ���ˇ�ĽY�ϣ�ͬ�r�����ӹ��y�ȣ��όӹ��̎�ڱ���,�������|���K�܇����όӹ��ƫ�x�������5 um,�_���Y��ጷŕr�γɿɄӲ������όӹ�֮�g����С�g����4 um��

����( 10) �Y��ጷţ� ���ϲ���Ƭ�M��ȥ�z����ϴ��̎�����όӹ�鱣�o�ӿ��g���g�����ӣ���ɽY��ጷš�

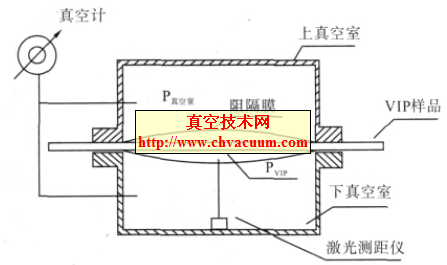

�����Ƃ乤ˇ���E��D2 ��ʾ��

�D2 �Ƃ乤ˇ���E

2�����yԇ

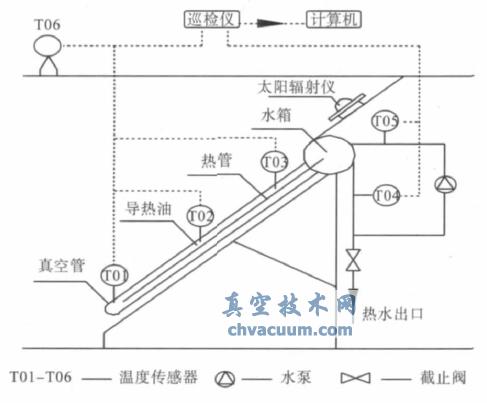

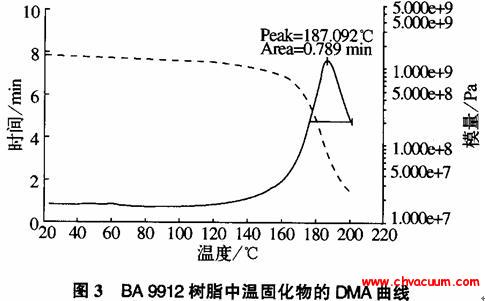

�D3 �yԇԭ��D

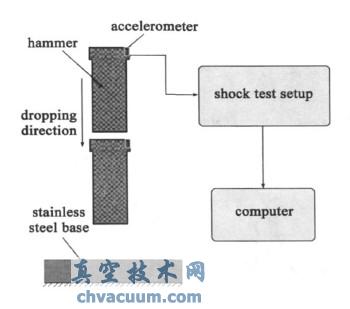

�����������ƵČ��yԇϵ�y�������OӋ���Ƃ��SOI ����g ֵ���ٶȂ������M���ˌ��yԇ����,�D3 �ǜyԇԭ��D�����yԇϵ�y���п�Ժ�Ϻ�ϵ�y�о���ᘌ������Ƶĉ���ʽ���ٶȂ��������Ƶģ����ڼ��ٶȂ������Y�����c������Փģ�ʹ��ڲ����ϵ�y�yԇ�M���˱�Ҫ��������ǰ���о��ѱ������������ڲ�ͬ���ٶ��d�ɗl���£�������׃����һ�£�����ͬ�d���g���ėl���£����Ȳ�������׃���g��Ҳ�������ֲ�׃���w�F�����õľ��Զȡ�ԓ���ٶȂ������Y���Ĺ����l�ʞ�479 kHz���ڸ��_25 × 104g ���ٶȕr��ԓ���ϵ��������544 MPa���hС���c����ϵĔ��я���0. 7~ 7 GPa�����C��ԓ���ٶȂ����������Ŀɿ��ԡ�

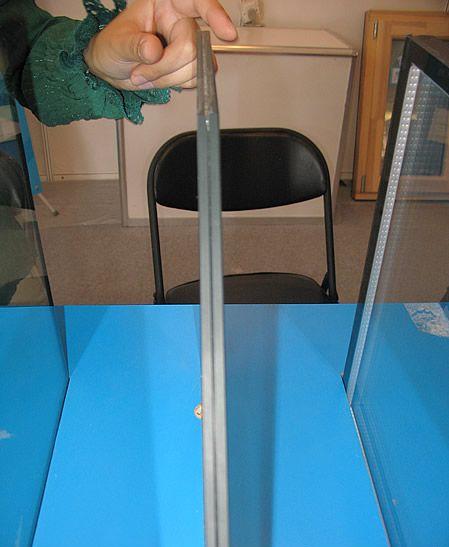

�����D4 �o�����½��߶ȷքe��75 ��35 cm �r���������ٶȷ����yԇʾ���D������һϵ�еĔ����������õ�ݔ��늉��c���ٶȵ�׃���Pϵ����D5 ��ʾ����Ҋݔ��늉��c���ٶ�֮�g�ľ��ԶȺܺá��������������ɵã�ԓ��g ֵ���ٶȂ��������`������1.170 LV/ g ��

�D4 �½��߶ȷքe��75 ��35 cm �r�����ٶȜyԇʾ���D�����D5 ݔ��늉��c���ٶȵ�׃���Pϵ

3���Y���Z

������������ICP �����g���g�OӋ�Ƃ���һ�NSOI ����g ֵ����ʽMEMS ���ٶȂ����������M���ˌ��yԇ��������������ԓ��g ֵ����ʽ���ٶȂ�����ݔ��늉��c���y���ٶ�֮�g�ľ��ԶȺܺã��yԇϵ�y���������`������1.170 LV/ g���M���OӋҪ���⣬���Ƃ���g�^����߀��ע�⣺

����(1) ICP ���g�У����ڿ��g�IJ������ԣ�ʹ�ÈAƬ�в��ֽY�����g�������ӣ����ֽY���]�У�����ʹ�������AƬ�еĽY�������g�������ӣ���������_�������ӵĽY���^�̣����ڿ��g���w�����ϵ��x���ԣ��Ķ�ʹ�ô������ӵĿ��g���w���߅�Uɢ�����footing Ч����

����( 2) �����ӵĺ������^�����øɷ����g�r��r�g�^�ã��Ķ����g�x�������������Z������Ҳ��ʹ�É������l�����g��һ���֣������pС�����ӵĺ�ȡ�����Ý��g�t�����γ�𤸽Ч��,�ұ�ǻ�����M���gҺ�p�ĽY����