ICP���g4H-SiC�Ų۹�ˇ�о�

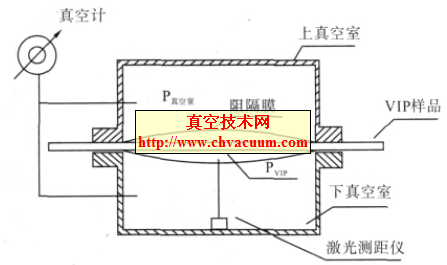

��������������Ĥ���������Ĥ�����IJ���SiO2���|������Ĥ��SF6/O2/Ar������g���w�����øБ���ϵ��x���w���g(ICP)���g��4H-SiC trench MOSFET�Ųۿ��g��ˇ�M�����о�������Ԕ���о���ICP���g�IJ�ͬ��ˇ�������g���ʡ����g�x����Լ����g��ò��Ӱ푡����Y��������SiC���g�����S��ICP���ʺ�RFƫ�����ʵ���������ӣ��S�����w������������g�x��Ƚ��ͣ����S�����⺬������ߣ����H���g�x����������܉���Ч�������ϲ�Ч�������g�Ų���ò�ͱ���ֲڶȷքeͨ�^��������@�R��ԭ�����@�R�M�б������@���˃����ĖŲ۽Y����RMS����ֲڶ�<0.4nm��

��������SiC���Ќ�����(2.3��3.3eV)�����R�����늈�(3×106 V/cm)��������Ư���ٶ�(2×107 cm/s)���ߟጧ��(4.9 W/(cm· K))�ȃ��c��ʹ��SiC�������Ƃ���ʡ��ߜء����l����ݗ��İ댧�w�����ȷ�����ИO��V���đ��á�

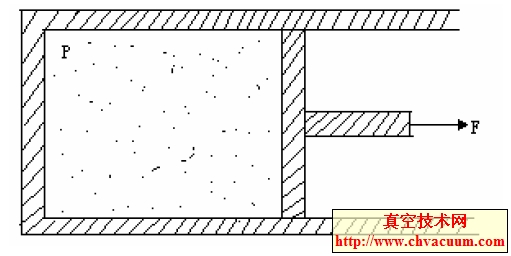

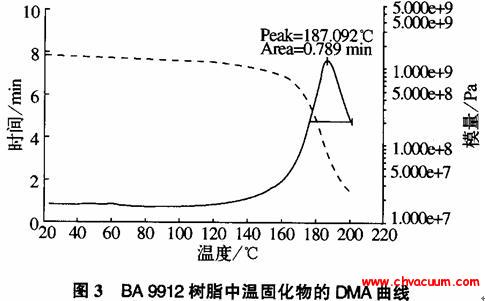

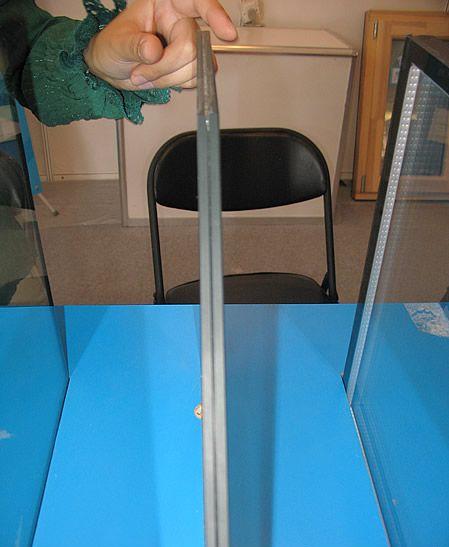

����Ȼ����SiC����Ӳ�ȸߡ����W���|�������y��ͨ�^���g�γɸ��N�Y����Ŀǰֻ�ܲ��øɷ����g�ķ���������SiC�ۖŽY��������UMOSFET��Trench Gate IGBT�Լ�SiC MEMS���������S�Y�����������g��ò�����g�p���Լ����g���暈����Ⱦ���SiC���������Ƽ������кܴ��Ӱ푡�Ŀǰ���gSiC��õĚ��w��F�����w����CF4��SF6�����Ό�������SF6/O2/Ar������g���w�����ڲ��ý�������Ĥ�������ڿ��g�^���н��ٴؕ��R�䵽SiC���棬�����ٿ��g�����hС��SiC���g���ʣ��Ķ������ڵ��γɣ�����������ĤЧ���Լ��������ٵ���Ⱦ�����������˸߶�ֱ��SiO2���|������g��Ĥ��ͨ�^������R(SEM)�^�y��ԭ�����@�R(AFM)�^�y�l�F���g����ܹ⻬�������RMS����ֲڶȞ�0.36nm��δ���F��Ĥ��ͨ�^�{�����g���������Ԍ��F�߿��g�x��ȵ�SiC���g��

������SiC�Ŀ��g��ˇ�У��������“�ϲ�”��ԓ��ˇ�е��y�c���ϲ�ָ���R���ȱڵĵײ��γɵ�V�ΰ��ۣ�����Ҫ������ԓ̎���g����������ɵģ��ϲ۵Ĵ��ڕ�����������늈����У����������ķ����ԺͿɿ��ԣ����Č��ϲ����������M����̽������K�@���˸߿��g���ʡ��߶�ֱ�ԡ��߿��g�x��ȡ��o�ϲ��ҵ��_�A���ĖŲۿ��g��ˇ�l����

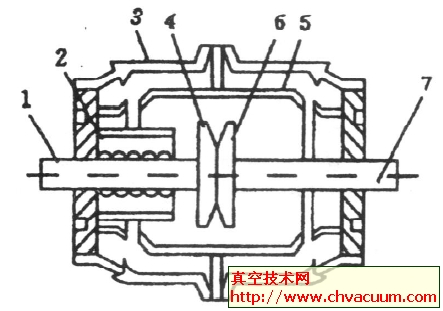

����1�����E

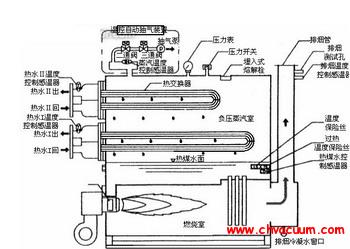

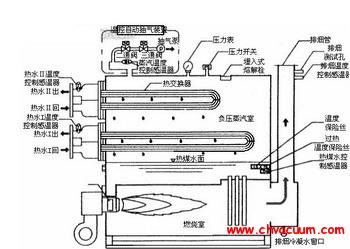

������������4H-SiC�r��������g���ϣ�����Ҏ��ϴ�����x���������W������e(PECVD)���L2μm��SiO2����SiC���g��Ӳ��Ĥ��֮��LPCVD���L100nm�Ǿ��裬�˷Ǿ���������gSiO2����Ĥ�����g�D�Ξ錒��3μm �L�l�΅^���Ǿ����SiO2�Ŀ��g�քe����Lam Research ��˾��Rainbow 4420��Rainbow 4520����SiC�Ŀ��g���õ�Sentech��˾��SI500ϵ��ICP���g�C�������о���ͬ���g������SiC���g���ʡ����g�x��ȡ��ϲ۵�������Ӱ푣��x�������µĿ��g�l����ICP����׃��������400��800 W��ƫ�����ʞ�30��200W�����g������0.2��2Pa��ͨ�^��׃O2������ʹ��O2����׃��������10%��50%���о����⺬�������gЧ����Ӱ푡�ͨ�^SEMS-5500�^�y���g��ò�Ϳ��g��ȣ�����AFM �����˘�Ʒ���g�ı���ֲڶȵ�׃����r��

����3���YՓ

��������������Ĥ���������Ĥ�����IJ���SiO2������Ĥ��Ԕ���о��˲�ͬ��ˇ��������ICP���ʡ�RFƫ�����ʡ����������⺬���Ȍ�SiC�ۖŅ^��Ŀ��g���ʡ�SiC�cSiO2�Ŀ��g�x��ȡ����g��ò��Ӱ푡��о��Y��������ͨ�^�{��ICP���ʺ�RF���ʃ���SiC���g���ʣ���ͨ�^�{��������O2�����{�����g�x��ȣ����c�о��������ϲ۵ķ�������K�@���˸߿��g���ʣ��߶�ֱ�ԣ��߿��g�x��ȣ��o�ϲ��ҵ��_�A���ă������g��ˇ�l������ICP���ʞ�800 W��RF���ʞ�100 W�������҉�����0.4Pa��SF6/O2/Ar������15/45/30�Ŀ��g�l���£����g��ֱ�Ժã��ײ�ƽ�����o�ϲ��ҵ��_�A���Ŀ��gЧ�������g���ʼs500nm/min�����Č����|��SiC�Ų۹�ˇ�����N�Ų۽Y��SiC�������аl����һ�����b���x��